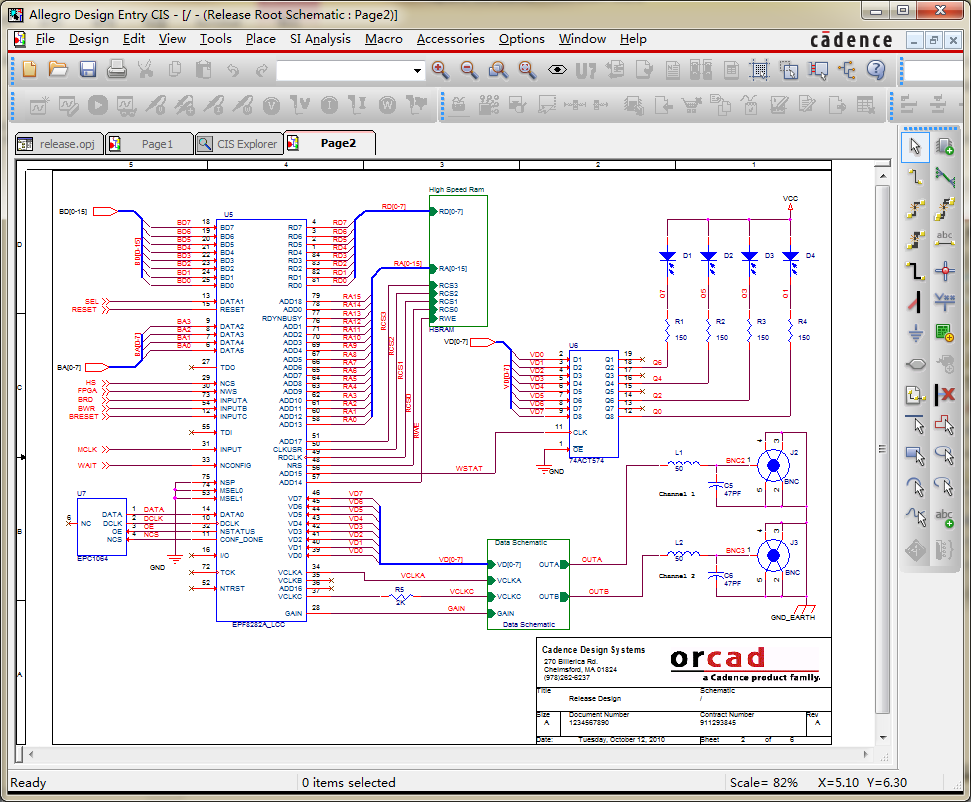

Capture CIS

Capture CIS提供了完整的、可调整的技术,应用于电路图的设计创建、管理和重用。将原理图设计输入功能与广泛的仿真和电路板布局技术相结合,Cadence能够帮助你一开始就抓住设计意图。

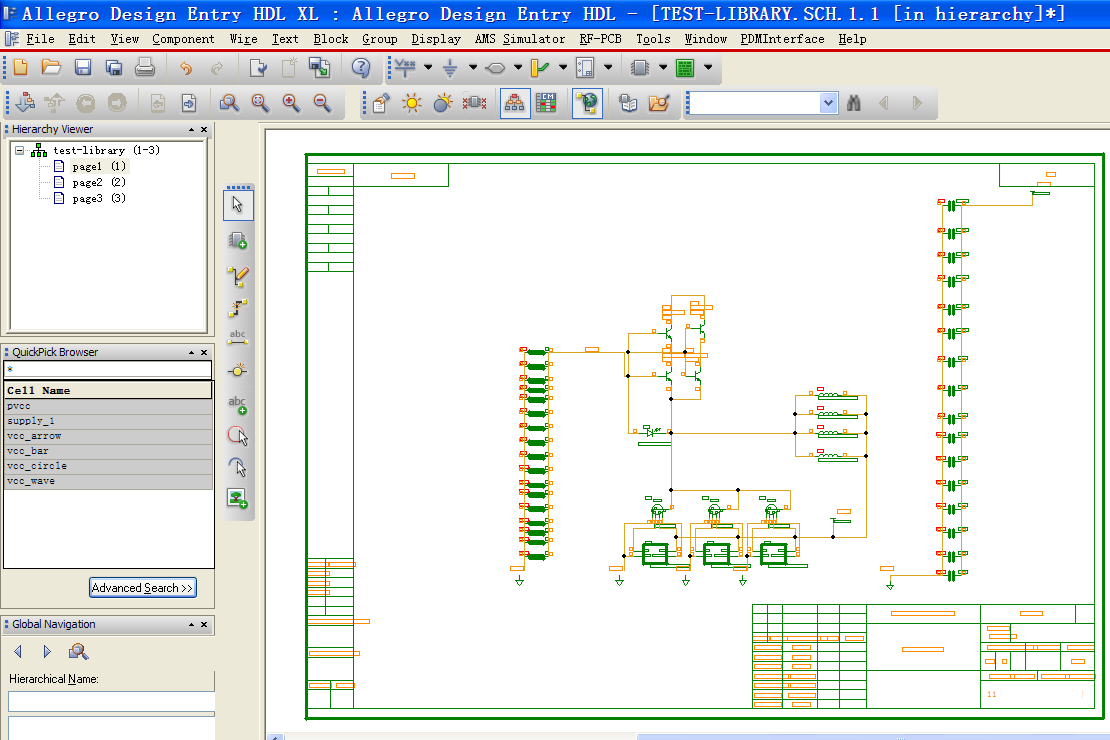

HDL

Allegro Design Authoring 提供了一种灵活的

原理图设计方案,能适应您不断变化的需要。它的企业级Schematic Editor 完美集成了Allegro AMS Simulator、

Allegro PCB SI Signal Explorer和 Simulator,以及 Allegro PCB Designer,使得约束驱动的 PCB

设计流程能用于可预测的数字、模拟、RF 与混合信号设计。

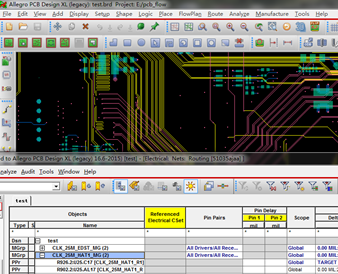

Allegro PCB Designer

Allegro PCB Designer是基础设计工具包,Allegro PCB Designer包含一个通用和统一的约束管理解决方案、PCB Editor、自动/交互式的布线器、以及与制造和机械CAD的接口。PCB Editor提供了一个完整的布局布线环境,适应从简单到复杂的各种PCB设计。

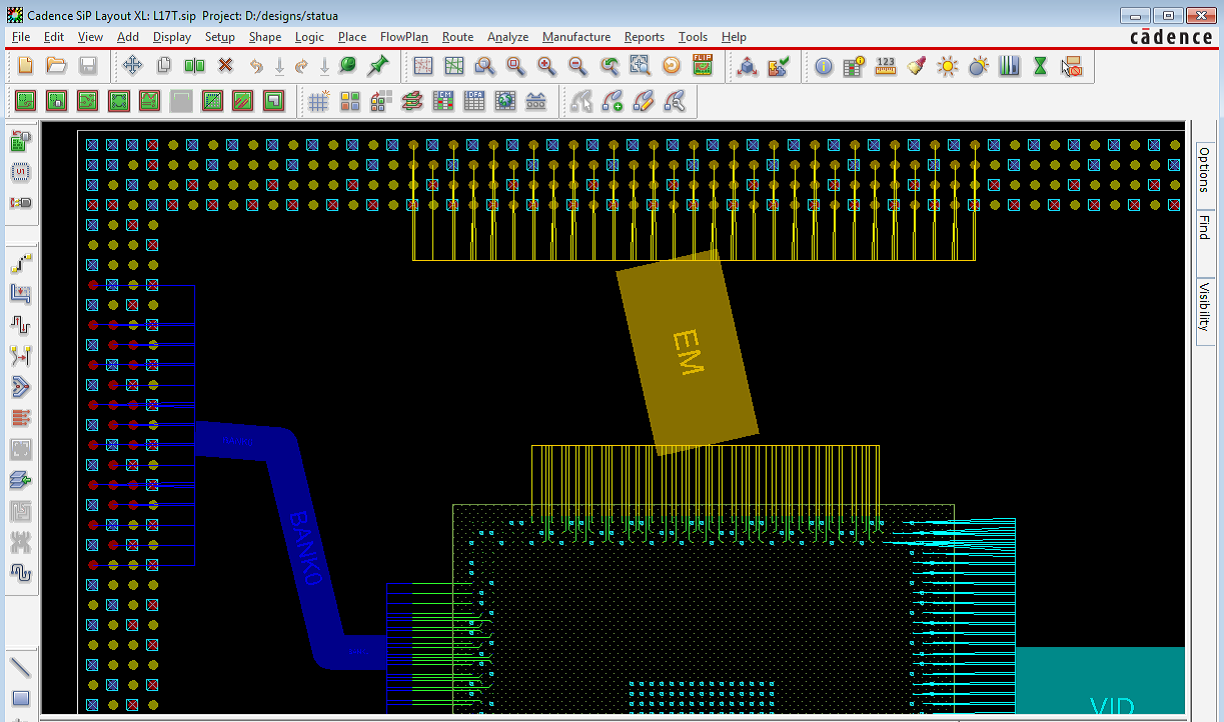

Cadence Sip 设计

SIP layout为封装基板设计工具,可以完成从简单到复杂不同层次的基板设计,能完成多IO管脚、高密度、多芯片堆叠、三维封装等复杂的封装设计,提供多重腔体、复杂形状封装形式的支持。支持所有的封装类型,包括QFP、PGA、BGA、CSP等封装类型。提供约束和规则驱动的版图设计环境。它包括布线、Wire Bonding、系统级设计优化、制造准备、整体设计验证。该环境集成了IC/封装/I/O布局性能、三维裸片堆叠结构生成与编辑性能。另外,完善的设计规则检查(DRC)可支持层压、陶瓷、及镀膜技术复杂和独特的要求。

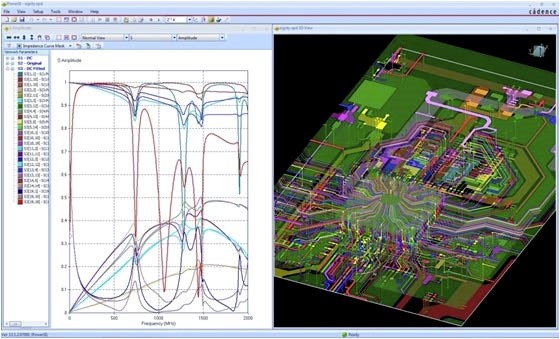

PowerSI

Cadence® Sigrity™ PowerSI™ 工具可以为IC封装和PCB设计提供快速准确的全波电磁场分析,从而解决高速电路设计中日益突出的各种电源和信号完整性问题,例如同步切换噪声(SSN)问题、信号耦合问题、去耦电容放置不当问题以及电压超标问题等。PowerSI可以方便的提取封装和PCB的各种网络参数(S/Y/Z),并对复杂的空间电磁谐振产生可视化的输出,能与当前主流的物理设计数据库如PCB、IC封装和系统级封装(SIP)进行无缝连接。

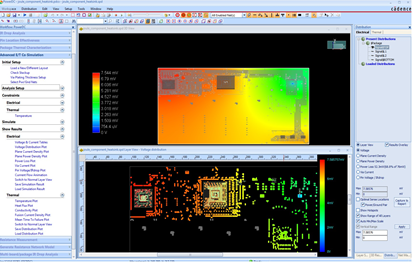

PowerDC

Cadence® Sigrity™ PowerDC™ 工具为IC封装和PCB 提供了快速、精确的直流分析,同时支持电热协同分析。 不管是布线前还是布线后, PowerDC提供了一个step-by-step的工作流程来发现隐含的IR Drop问题、电流密度和热的问题。这些过压、欠压和热问题可能导致系统故障并带来额外的产品成本。PowerDC能够快速的给出分析结果,同时带有感应线优化和DRC检查等高级功能。分析结果可以导出用于其它相关分析。

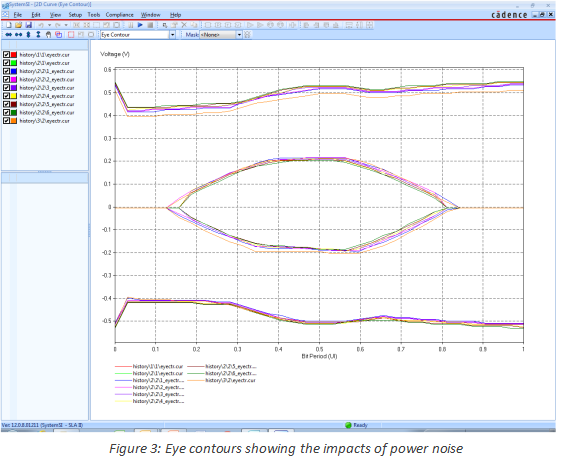

Cadence Sigrity SystemSI

Cadence® Sigrity™ SystemSI™ Signal Integrity Solutions提供了全面

和灵活的SI仿真环境,能够精确的分析高速、芯片到芯片的系统设

计。提供了易学易用的基于模块的仿真编辑器。支持业内标准的仿真

模型,并能自动创建模型间的连接关系。拥有业内的时频域相结

合的统计分析技术,设计师可以轻松完成稳定的高速并行总线和串行

链路的设计。

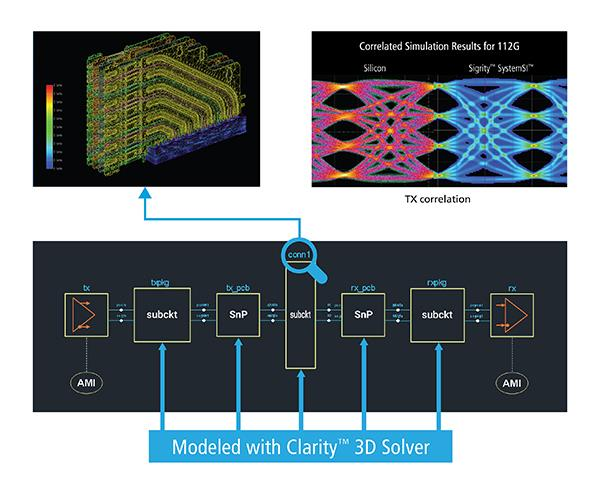

Clarity 3D Solver

Cadence® Clarity™ 3D Solver 是一款 3D 电磁(EM)仿真软件工具,用于设计

PCB、IC 封装和 IC(SoIC)系统设计的关键互连。Clarity 3D 求解器可让您在设计 5G、

汽车、高性能计算(HPC)和机器学习应用系统时,以黄金标准的精准性完成复杂的电磁

(EM)挑战。